背景

存储芯片大涨,就连模拟芯片也跃跃欲试。作为消费者如何看清其中门道,首先我们看看存储在半导体行业位置。

- 光电器件、传感器件、分立器件

- 光电器件:光电管、光电倍增管、光敏电阻、光敏二极管、光敏三极管、光电池、光电耦合器件等

- 传感器件:MEMS 传感器、超声波传感器、激光传感器、红外传感器

- 分立器件:晶体二极管、三极管、晶体管

- 集成电路

- 模拟芯片:电源管理芯片、信号链芯片和射频芯片

- 微处理器:CPU、MCU、SOC

- 逻辑芯片:DSP、ASIC、FPGA 等

- 存储器:DRAM、FLASH

这是从业者的行业分类来看的,很显然其实对于我们普通消费者来说,上面一堆,我们最关注的就是CPU、FLASH,一些发烧友可能对模拟芯片也比较有兴趣。作为一个非硬件行业从业者,本篇文章也是由消费者角度来,从发展历程、国家博弈到具体SPHBM4、UFS 5.0协议规范发布来观察行业发展,以此来理解当前的行业现象和发展方向。

发展史

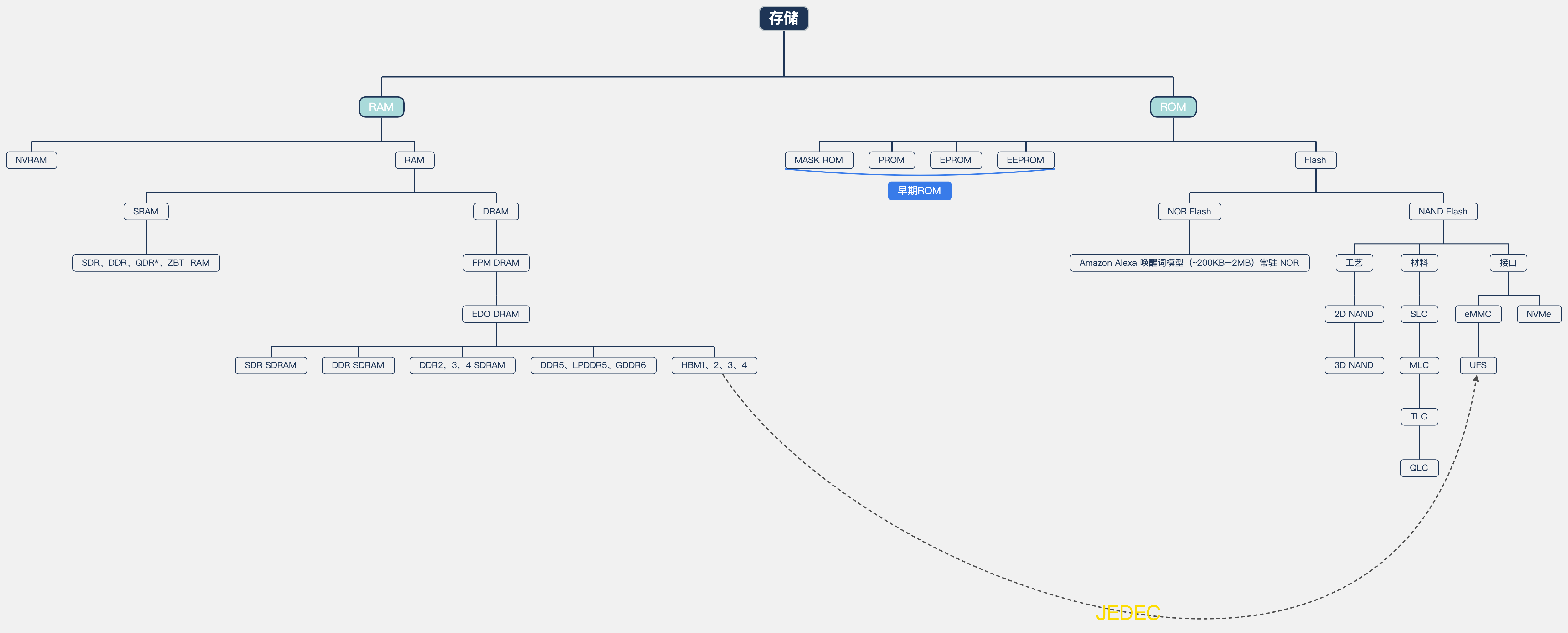

在谈论存储器历史前,我们先大概梳理下存储器、半导体、集成电路几个词的概念。当下的存储器一般是一个控制芯片加上一个存储芯片。但是这个是集成电路普及的今天的样子,在只有半导体没有集成电路时代,存储器可以是真空电子管;而在半导体也没有出现的时代,存储器可以是磁鼓、磁芯甚至打孔纸带。存储器作为一个功能性突出的工具伴随着计算机技术的发展其内涵也在不断变化。 存储器分为:RAM 随机存取存储器和ROM 只读存储器。后面将从这两个分类,根据市场、技术的分类展开讲讲,因为这两个分类在早期(20 世纪 50 年代集成电路发明后)就有明确的分界线,同时主要参考市场分类,因为作为一个产业主导的行业,以技术分类其实有时候没有什么意义(例如NVRAM( Non-Volatile Random Access Memory) 技术上的分类很容易理解,但其实基本没有市场划分的产品)。 而在这两个类别分野前,值得一提的还有磁鼓存储器(1932 年,Gusta Tauschek 发明)、威廉姆斯 - 基尔伯恩管(1949 年,弗雷迪・威廉姆斯和汤姆・基尔伯恩发明,曼切斯特1型(Manchester Mark 1))是最早的实现冯·诺伊曼结构的计算机之一)、磁芯存储器(20 世纪 50年代,美籍华人王安发明)。同时磁存储作为如今依旧以机械硬盘作为代表的重要存储技术,严格来说并不属于半导体产业,也不作为本篇的主体。

RAM随机存取存储器

NVRAM( Non-Volatile Random Access Memory)非易失性随机存储器

非易失性随机存储器(NVRAM)是一种即使在断电后也能保留数据的存储器。 主要技术类型

- 磁阻式随机存储器 (MRAM): 利用磁性存储数据,速度接近 SRAM,功耗低,寿命长。

- 铁电随机存取存储器 (FRAM): 利用铁电材料的双稳态特性,读写速度快,耐久性高。

属于明显的技术类别分类,因为没有搭乘上集成电路的技术东风,难以在消费领域铺展开来。

RAM(Volatile Random-access memory)随机存取存储器

SRAM(Static Random-access memory)静态随机存取存储器

| 特性 | CPU 寄存器 | 片上缓存 (L1/L2) |

|---|---|---|

| 实现技术 | CMOS+6T-SRAM | CMOS+6T-SRAM |

| 访问速度 | 0.1-1ns | 1-10ns |

| 功耗密度 | 极高 (单位 bit) | 高 |

| 位置 | CPU 内核内 | CPU 芯片内 |

开始和Dram都是主存,后来变成高速缓存。通用领域转向CPU缓存、FPGA等专用高速应用。现在主要应用场景就是片上缓存。

DRAM(Dynamic Random Access Memory)动态随机存取存储器

相对于6 晶体管的SRAM,一个晶体管+一个电容单元,结构简单方便大规模集成。 经历了从基础单元(晶体管+电容)实现高密度存储,到同步化(SDRAM)和双倍速率(DDR)技术提升速度,再到追求更高带宽、更低功耗的DDR2/3/4/5(主流)演进,而现在正向DDR6(未来)和3D DRAM (垂直堆叠) 探索,以突破传统平面微缩的物理极限,满足人工智能和高性能计算对带宽和密度的需求。关键是制程微缩(1α, 1β, 1γ等节点)和架构创新(DDR、LPDDR、HBM、3D DRAM),以实现性能飞跃。

当前发展:

DRAM 种类当前主要包括 DDR5、LPDDR5X、GDDR6X 和 HBM3E,**差异主要在于外围电路设计,而内存单元和制造工艺相似。**每种针对不同应用优化:

- DDR5:采用 DIMM 封装(也就是我们最终看到的内存条),提供最高容量,适合服务器和高容量需求,但功耗较高、成本随容量增加而上升。

- LPDDR5X:低功耗设计,需要短距离连接,容量受限,主要用于手机、笔记本。近年来扩展到 AI 加速器和高效 CPU(如 Nvidia Grace,容量可达 480GB/托盘),作为“第二层”内存,提供高能效和大容量(比 GDDR 高 10 倍),但通道多导致布局拥挤、ECC 支持弱(需牺牲部分容量用于纠错)。

- GDDR6X:图形专用,高带宽、低成本,但延迟/功耗高、容量受板级限制,适合游戏 GPU,不宜大规模 AI 应用。

- HBM3E:高带宽内存,宽总线(1024 位/封装)和垂直堆叠(8-12+ 层,使用 TSV 通孔),提供极高带宽密度、最佳每比特能效和真正 ECC。缺点是成本极高(因堆叠复杂、产量低),主要供应商 SK Hynix 领先,三星/美光产量挑战大。

在 AI 加速器中的比较与应用

- HBM3E 是大型 AI 加速器(如 Nvidia H100、AMD MI300X)的首选:带宽、能效和可靠性无可替代。尽管昂贵且供应紧张,仍是最有价值的产品,AI 需求持续推动增长。

- GDDR6X 次之,容量小、功率高,适合中小规模 AI。

- LPDDR5X 和 DDR5 表现较差,不适合高强度加速器需求(能效低、带宽不足)。

- 即将 LPDDR6 改进有限(通道数高、速度提升小、ECC 弱),无法挑战 HBM。

当前HBM 在带宽、密度、能效和 ECC 上主导 AI,但扩展困难:堆叠需求导致芯片尺寸大、TSV 布线复杂、产量低(三星曾因节点落后产量低,SK Hynix 通过先进封装领先)。尽管新供应增加可能降低利润率,AI 对内存需求爆炸式增长将抵消影响。目前无其他 DRAM 可替代 HBM,导致行业依赖其高成本解决方案。

ROM只读存储器

早期的ROM(read-only memory)

MASK ROM、PROM、EPROM、EEPROM,只有MASK ROM是只读的,后面的技术发展,基本已经脱离字面含义了,形成自己独特的含义代表了。

Flash(flash memory)

闪存在分类上属于EEPROM的一种,闪存又分为NOR与NAND两型。

NOR Flash

nor flash 属于flash ROM的自然发展,因为ROM早已不是只读的,但还是主要用于存储几乎不需更新的代码,例如电脑的BIOS或机顶盒(Set-top Box)的固件。现在(2025年末)nor flash的应用场景依旧是在较低更新频率场景,例如Amazon Alexa 唤醒词模型(~200KB–2MB)常驻 NOR。

NAND Flash

可以从工艺、材料、接口三个维度分类。 工艺类。 2D 平面工艺 细胞在单一平面层排列,使用光刻缩小节点大小(从微米级到10nm级)。早期主流,依赖多重图案化(如三重/四重图案化)来实现小于20nm节点。 3D 垂直堆叠工艺 细胞垂直堆叠多层(从24层到超过200层),使用高深宽比(HAR)蚀刻通道孔和楼梯结构。节点大小放松(等效10-20nm),但层数决定密度。 材料类。 浮栅材料 (Floating Gate) 使用多晶硅层存储电荷,通过隧道氧化物(SiO₂)注入/释放电子。适用于2D结构,但缩放时易漏电。 电荷陷阱材料 (Charge Trap) 使用硅氮化物(SiN)层捕获电荷(如SONOS/TaNOS结构),取代浮栅。常见于3D NAND,结合高k介电质(如ZrO)。新兴材料包括InGaAs通道(高迁移率)和铁电材料(HZO,低功耗)。 细胞类型分类 根据每细胞位元数:SLC (1位)、MLC (2位)、TLC (3位)、QLC (4位)。材料优化如空气间隙(Air-Gap)或低k层减少干扰。 协议类。 以2012年为界限从 ONFI 主导到 JEDEC 主导,ONFI 专注于 NAND 接口,而 JEDEC 覆盖更广(如 DRAM、eMMC),便于生态整合。当然还有苹果独家的NVMe。

结尾

存储设备,作为消费电子领域仅次于CPU能被感知的大规模集成电路应用,其前沿的技术发展和消费市场一直都是紧密相连的,所以其模糊的产品名词分界也是源于其快速变化的技术与市场博弈。但是AI浪潮又一次的把这个博弈的平衡打破了,也将会是新一轮产业革命的起点。